저번 시간까지 Linux 사용법에 대해 알아봤다면, 이제부터는 Virtuoso 사용법에 대해 알아보도록 하겠습니다.

<전체적인 과정>

1. Circuit Schematics 만들기

2. Spice Netlist 추출

3. Hspice input deck(.sp file) 작성:

▶ 2023.10.11 - [아날로그 IC설계] - Linux(리눅스) 사용법 - 3. Hspice netlist(input deck) 작성법_sp file

4. Simulation(Hspice run)

● Virtuoso란?

Cadence 사의 Circuit schematic editing / layout editing / simulation용 EDA Tool입니다.

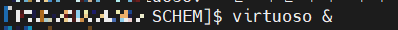

1. Virtuoso 실행

virtuoso & 작성

* 반드시 .cdsinit, .cdsenv, cds.lib가 있는 곳에서 실행해야 합니다.

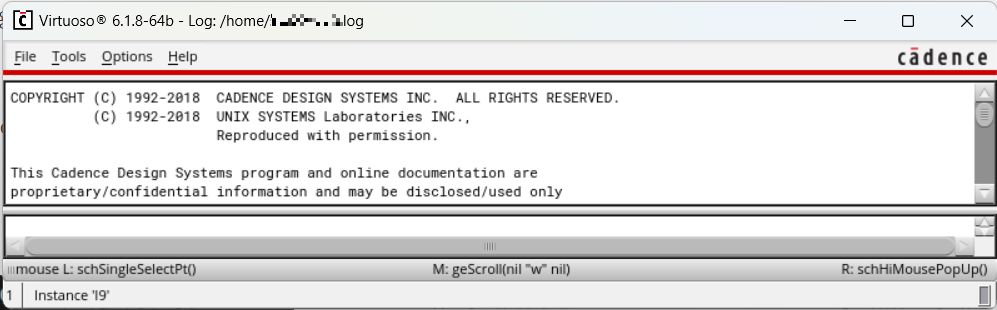

그럼 아래와 같은 CIW(Command Input Window) 창이 뜹니다.

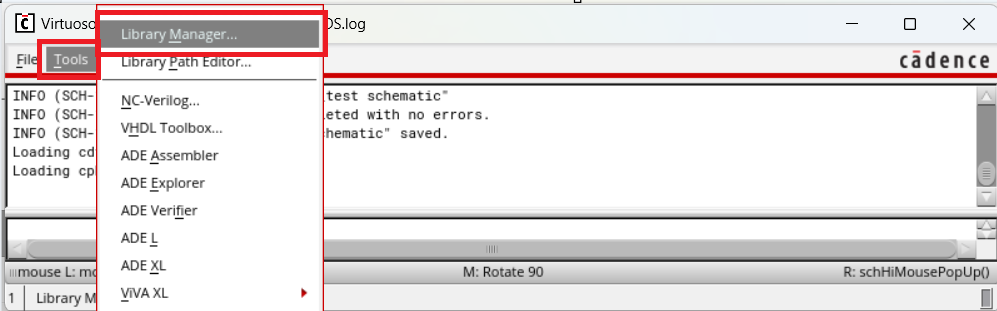

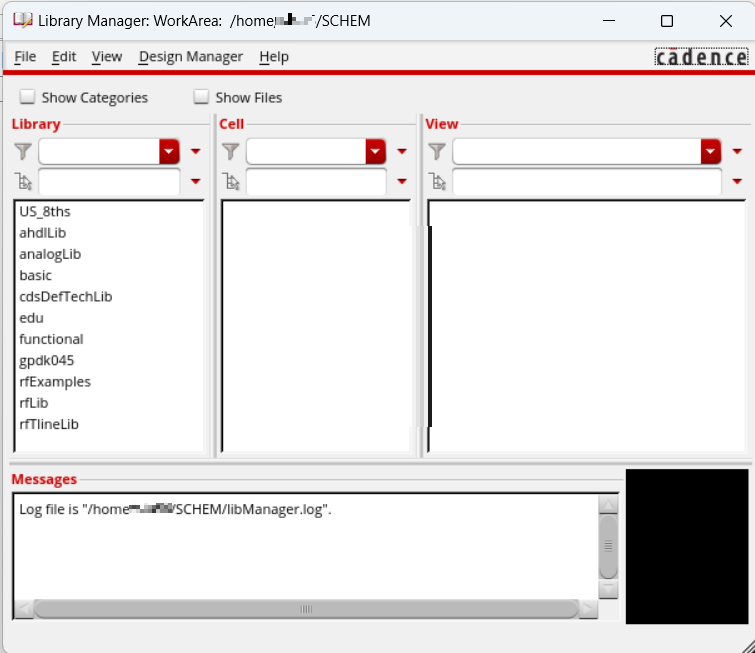

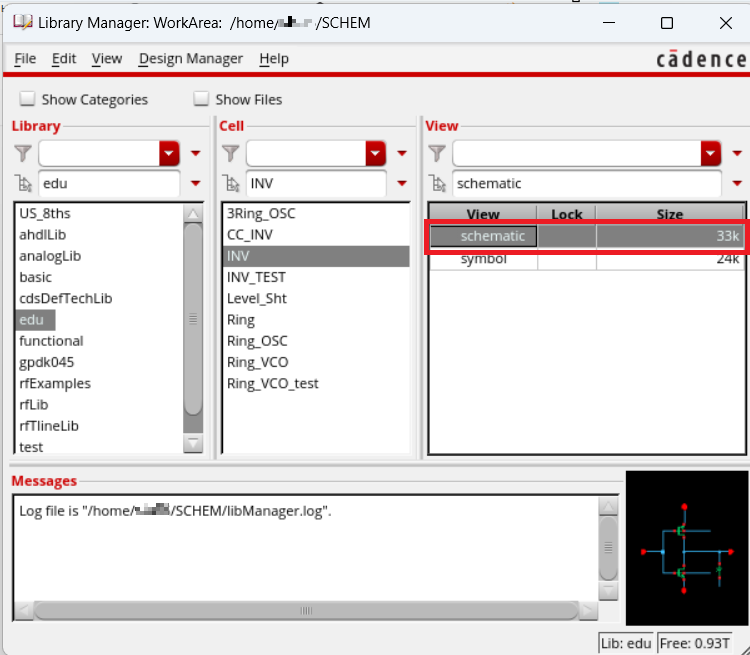

2. Open Library Manager

CIW window 창 → Tools → Library Manager

아래와 같은 Library Manager창이 뜹니다.

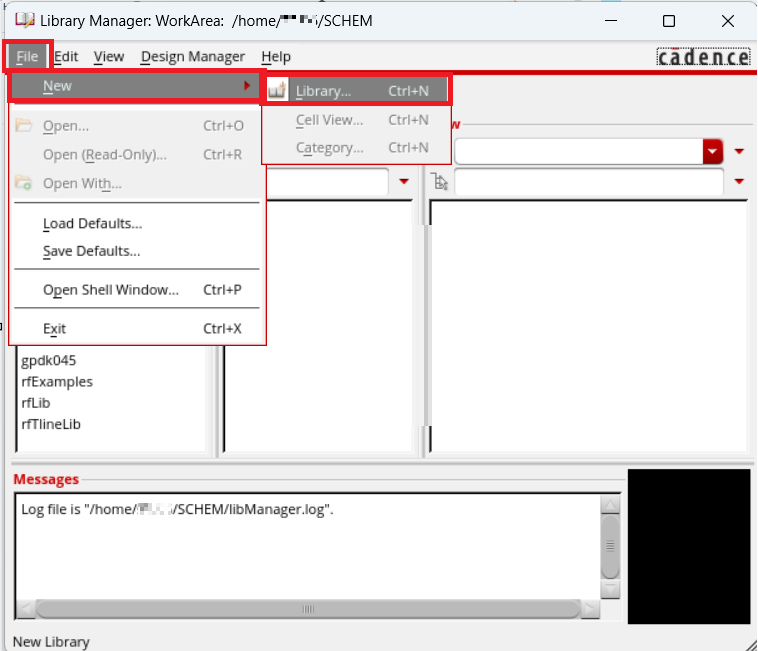

3. Create Design Library

Schematic을 만들기 위해 Design Library를 생성해야 합니다.

Library manager → File → New → Library

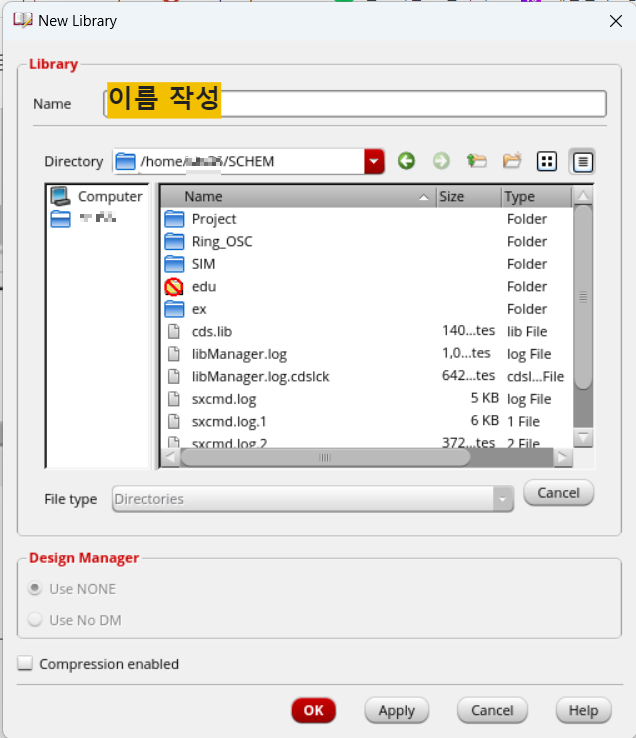

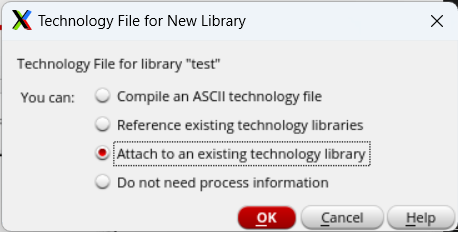

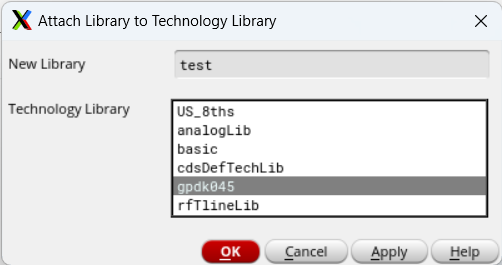

4. Attach technology library

필요한 소자들을 사용하기 위해서 특정 libraray를 attach해주어야 합니다.

1) New Library Name 작성 - OK

2) Attach to an existing technology library 체크 - OK

3) 원하는 lib(gpdk045) 클릭 - OK

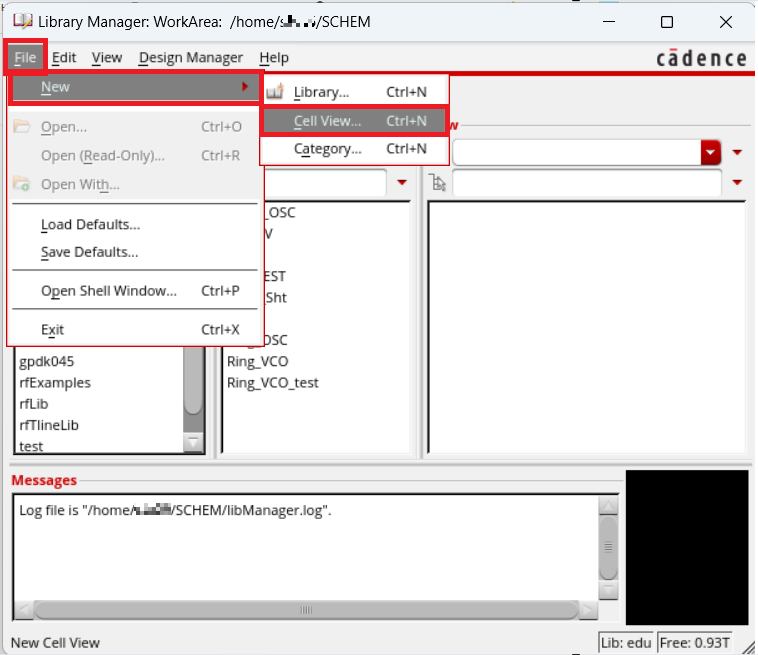

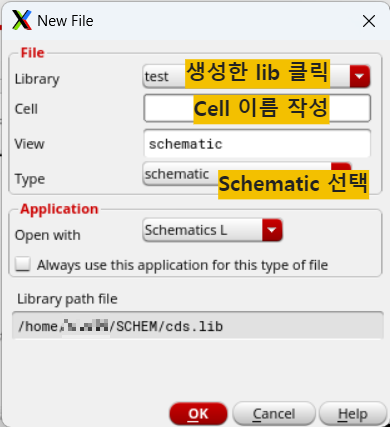

5. Create Cell View

이제 Schematic을 그릴 cell을 생성해야 합니다.

다시 Library manager → File → New → Cell View

아래와 같은 창이 뜨면, 4번의 과정에서 생성한 lib 클릭, cell 이름 작성, type은 schematic으로 설정하고 OK.

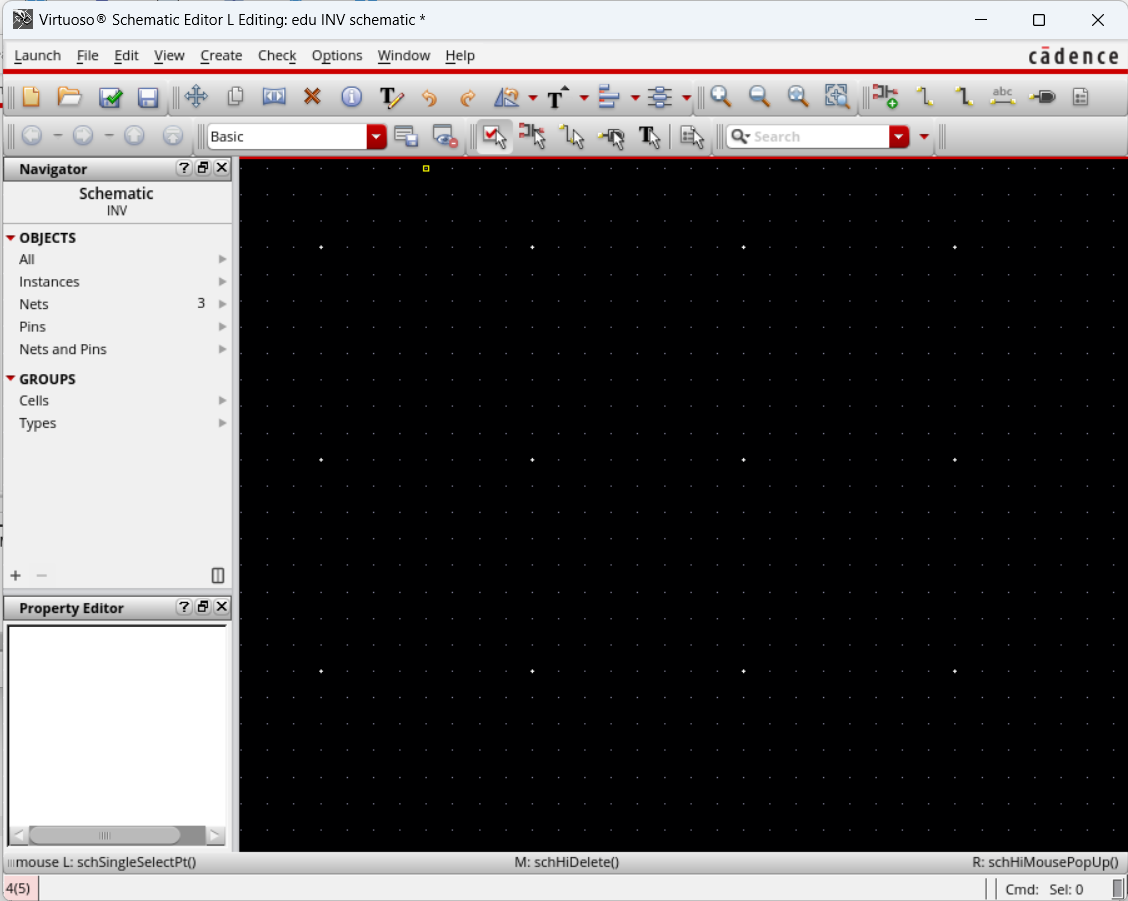

6. Open Schematic

정상적으로 cell이 생성됐을 시, 다음과 같이 GUI 창이 뜹니다.

안뜰 경우, 아래와 같이 Library Manager에서 해당 cell 더블클릭 해주면 됨!

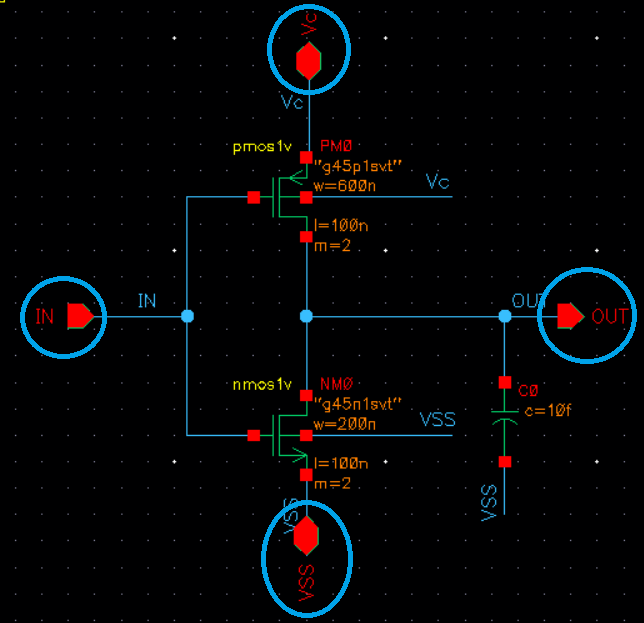

6. Create Instance

이제 GUI 창에서 소자를 추가하여, schematic 그려주면 됩니다.

자주 쓰는 단축키들을 설명하자면,

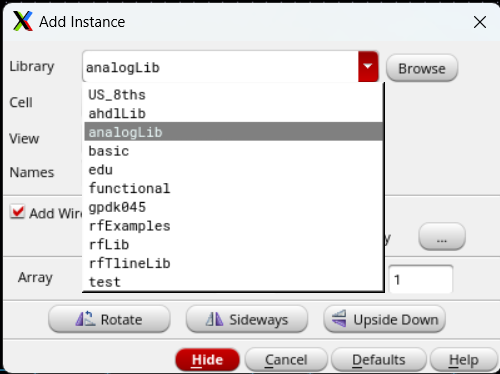

● i : 소자 불러오기

Res / Cap / Vdd / Vss와 같은 기본적인 것들은 analogLib에 존재

45nm 공정 nmos나 pmos를 사용할 경우에는, 위에서 attach해준 gpdk045에 들어 있습니다.

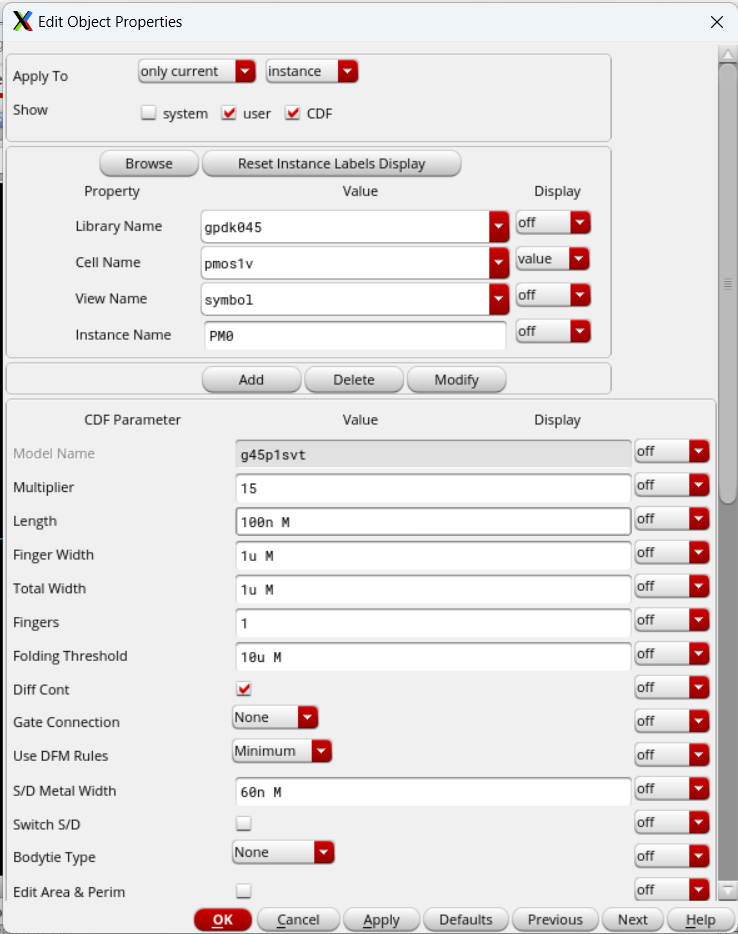

● q : 소자 특성 변경

변경하고픈 해당 소자 클릭 후 q 입력

M / L / W 등 변경 가능

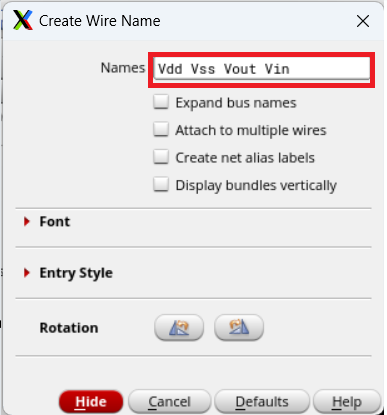

● l : wire name 추가

wire name으로 wire간 연결 가능합니다.

* name 입력 시, 띄어쓰기로 여러 wire name 동시 생성 가능합니다.

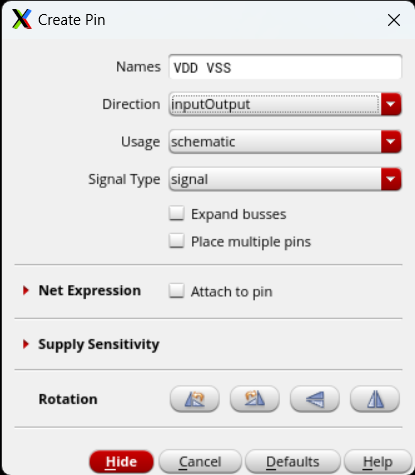

● p : pin 추가

schematic 구성 후에, Pin 설정을 해주어야 해요.

p를 누르면 다음과 같은 창이 나옵니다.

Input은 Direction→Input

Output은 Direction →Output

Vdd나 Vss는 Direction →InputOutput으로 설정해주면 됩니다.

* name 입력 시, 띄어쓰기로 여러 pin name 동시 생성 가능합니다.

● Virtuoso 단축기

| 단축키 | 내용 |

| i | Instance 추가 |

| w | Wire 추가 |

| l | Wire name 추가 |

| p | Input/Output Pin 추가 |

| q | 선택된 properties 수정 |

| c | 복사 |

| m | 이동 |

| u | 한 단계 전으로 undo (ctrl+z의 기능) |

| U | redo |

| f | zoom to fit |

| Shift+x | 저장 |

| r | rotate shift+r : 좌우반전 / ctrl+r : 상하반전 |

| m | wire 연결 유지하며 cell 이동 (shift+m : wire break) |

* 해당 기능 종료 원할 시, ESC

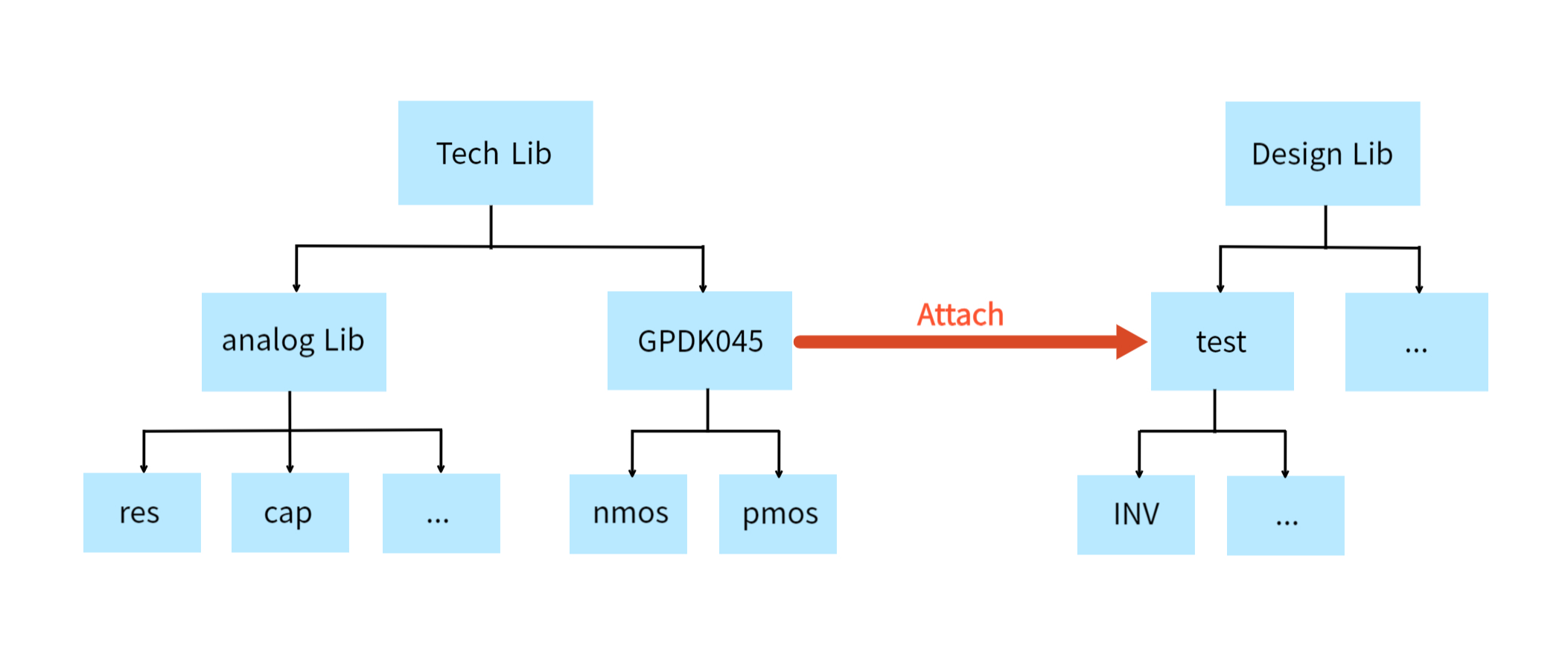

▶ Attach technology library과정이 필요한 이유:

Cadene Library 구성은 다음과 같습니다.

● Technoloy Library:

- analog Library: Cadence에서 기본적으로 제공하는 technology library로 cap, res, vss, vss 등의 기본소자가 들어있다.

+) gpdk 90nm, gpdk 45nm 등의 pdk가 존재

● Design Library는 내가 그리는 schematic이 들어가 있습니다.

그렇다면 위와 같이 attach의 과정을 해주는 이유는?

예를 들어 위의 그림처럼 test라는 library를 내가 만들었다고 하고, 거기에 inverter schematic을 GPDK045안의 소자들을 이용해 그리고 싶다면, GPDK045와 현재 나의 test lib을 attach해주어야 합니다. 즉, GPDK045 안의 소자들을 내가 끌어와서 쓰는거에요.

내용이 생각보다 길어져서, netlist 추출 방법은 다음 포스팅으로 찾아오도록 하겠습니다:)

'아날로그 IC설계' 카테고리의 다른 글

| Linux(리눅스) 사용법 - 3. Hspice netlist(input deck) 작성법_sp file (0) | 2023.10.11 |

|---|---|

| Linux(리눅스) 사용법 - 2. VI Editor(sp file 작성) (0) | 2023.10.09 |

| Linux(리눅스) 사용법 - 1.기초 명령어 (1) | 2023.10.08 |